数字部分 1 环境讲解和 PC Ie Ip配置

PCIe SerDes 全流程实战

数字部分——环境讲解和PCIE IP配置

1 环境介绍

1.1 参考文档

- Synopsys PCIe IP Controller User Guide(PCIe 控制器 IP 用户手册)

- Synopsys PCIe IP EP Databook(Endpoint 手册,内容较用户手册更为详尽)

- Synopsys PCIe IP EP Registers(寄存器手册,供驱动开发使用)

- PCI Express Base Specification Revision 4.0, Version 1.0(PCIe 标准文档)

- PCIe SVT Doc(PCIe VIP UVM 验证文档)

- PCIe AMBA Doc(AMBA VIP UVM 验证文档)

- Synopsys VCS 工具文档

- Synopsys Verdi 工具文档

1.2 工具说明

-

PyCharm 编辑器

由于虚拟机环境为 CentOS 7,不便使用新版 VS Code,因此选用 PyCharm。

安装 System Verilog Studio 插件后,新账号可免费试用 30 天。cd /home/jjt/Downloads/pycharm-2025.1.1.1/bin sudo ./pycharm -

VMware 虚拟机

可从官网下载最新版,个人使用免费。 -

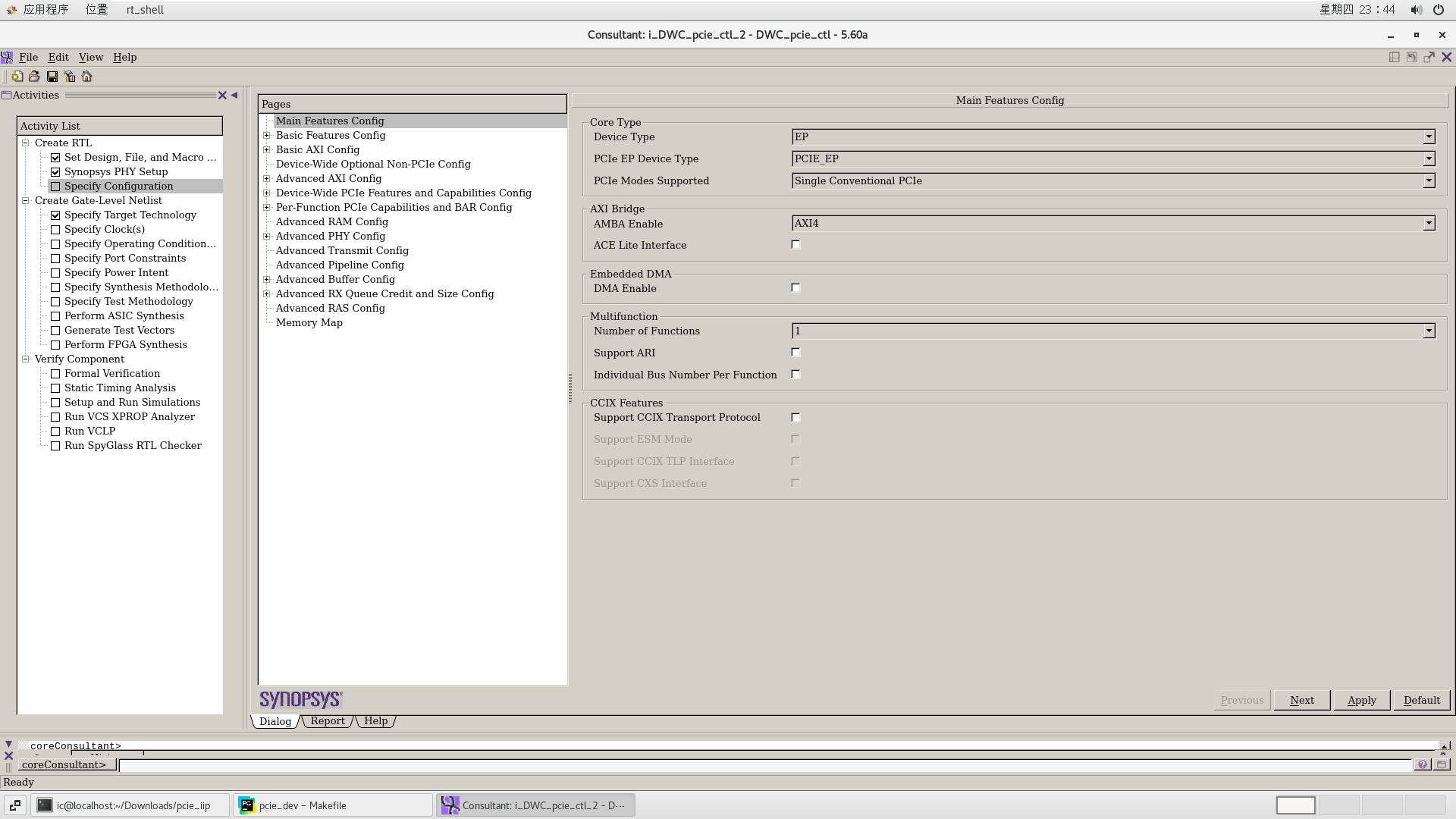

Synopsys coreConsultant — 用于配置 Synopsys PCIe Controller IP

export DESIGNWARE_HOME=/home/jjt/Downloads/pcie_iip /home/jjt/Downloads/coretools/T-2022.06/bin/coreConsultant -

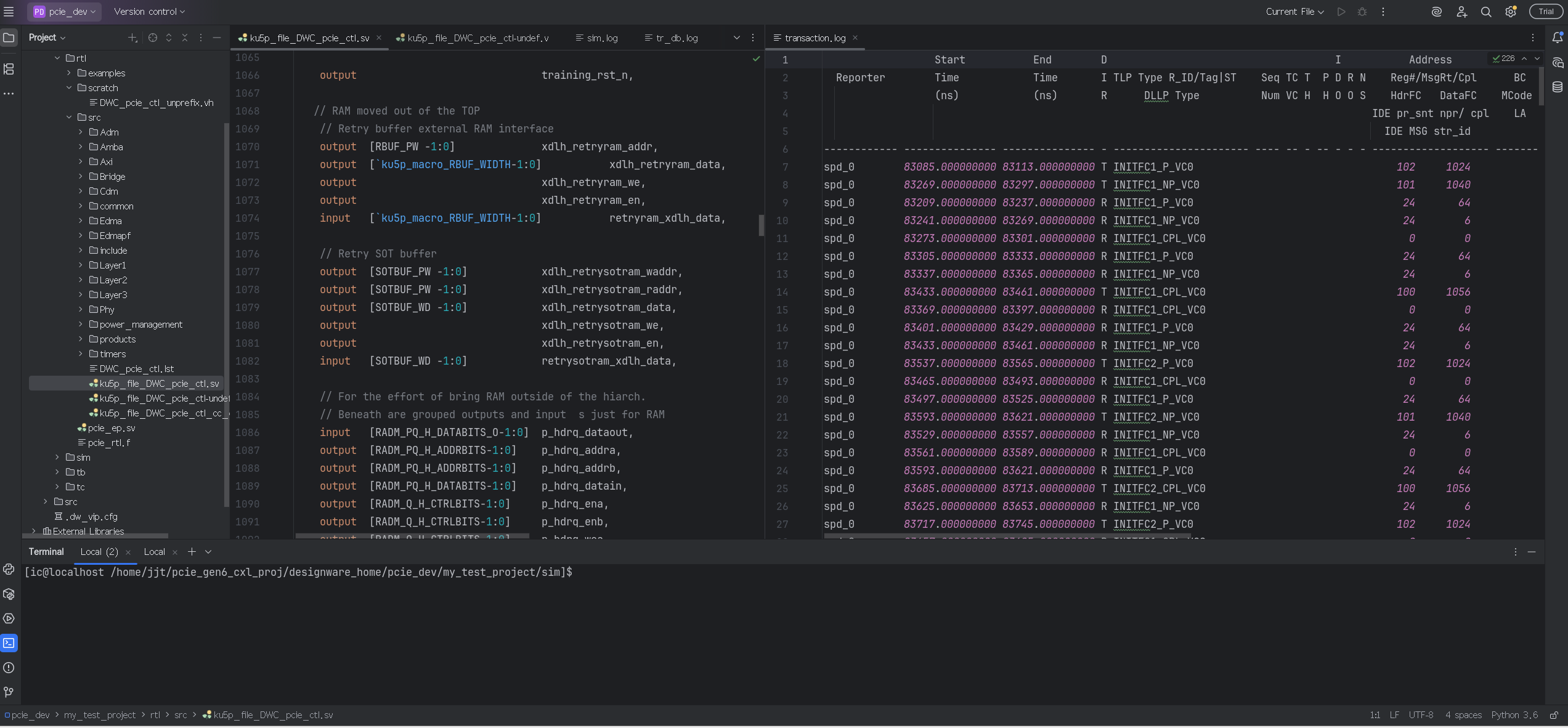

Synopsys VCS — 高速 SV/Verilog 仿真调试平台,支持覆盖率分析与并行仿真

vcs -l compil.log -lca -ntb_opts uvm-1.2 \ +incdir+/home/jjt/pcie_gen6_cxl_proj/designware_home/pcie_dev/include/verilog \ +incdir+/home/jjt/pcie_gen6_cxl_proj/designware_home/pcie_dev/include/sverilog \ +incdir+/home/jjt/pcie_gen6_cxl_proj/designware_home/pcie_dev/src/verilog/vcs \ +incdir+/home/jjt/pcie_gen6_cxl_proj/designware_home/pcie_dev/src/sverilog/vcs \ -y /home/jjt/pcie_gen6_cxl_proj/designware_home/pcie_dev/src/verilog/vcs \ -y /home/jjt/pcie_gen6_cxl_proj/designware_home/pcie_dev/src/sverilog/vcs \ +define+UVM_PACKER_MAX_BYTES=8192 +define+SYNOPSYS_SV +define+SYNOPSYS_TIMESCALE \ -Mupdate -sverilog -full64 -debug_access+all -top tb_top \ +warn=RT-NCMUCS +warn=UII-L +warn=TFIPC -timescale=1ns/1ps \ +libext+.v+.sv +define+RAM_INIT=0 \ +incdir+../rtl +incdir+../rtl/src +incdir+../rtl/src/include \ +incdir+../rtl/src/Phy/generic -f ../rtl/pcie_rtl.f \ +incdir+.. +incdir+../tb ../tb/tb_top.sv ./simv -l sim.log +ntb_random_seed=0710070742 \ +warn=noRT-NCMUCS +warn=noUII-L +warn=noTFIPC \ +UVM_VERBOSITY=UVM_LOW +UVM_TESTNAME=pcie_mem_pkg_test \ +UVM_TIMEOUT='8000,YES' -

Synopsys Verdi — SoC 设计调试及波形查看平台

verdi -sv -nologo \ +incdir+../rtl +incdir+../rtl/src +incdir+../rtl/src/include \ +incdir+../rtl/src/Phy/generic -f ../rtl/pcie_rtl.f \ +incdir+.. +incdir+../tb ../tb/tb_top.sv \ -top tb_top -ssf pcie.fsdb & -

Synopsys waveutils — 波形格式转换工具,可配合 Python 等工具分析波形

waveutils --tool=2vcd extractSignal.fsdb -o extractSignal.vcd -

Make / Makefile — 构建工具,避免每次手动输入长命令

2 Synopsys PCIe IP 配置

为缩短仿真调试时间并减少后续 FPGA 时序风险,本项目采用简化配置。

2.1 Design Prefix

为全部代码与配置增设统一前缀,对功能影响较小。

2.2 Synopsys PHY

若使用配套 Synopsys PHY,可启用;亦可选择外部 PHY。

2.3 Main Features

-

Core Type

本项目定位为 Endpoint(EP):- device type = EP

- PCIe EP Device Type = PCIE_EP

- PCIe Modes Supported = Single Conventional PCIe

-

AXI Bridge:选择 AXI4

-

Embedded DMA:不使用

-

Multifunction:数量设为 1,其余选项不启用

2.4 PCIe Basic Features

- PHY Type:Custom PHY

- PHY / Core Config:PCIE GEN1 ×1,参考时钟 125 MHz

- PIPE Spec:PIPE 4.3

- PCIe 4.0 / 5.0 Features:本项目暂不涉及

2.5 Common Basic Features

- PCIe Max Payload:选 256 B(项目无需大数据包)

- Address Translation:不使用 PCIe IP 自带地址转换

- Technology

- FPGA 实现需联系 Synopsys 支持,ASIC 后端暂不使用

- Use External RAMs:勾选,将 RAM 接口暴露至 Top Module,提升灵活性

- Technology Speed:如目标为 FPGA,选择 slow

- 其余未列项保持默认或不勾选

2.6 Basic AXI Config

- Address / Data Width:32 bit(与 BAR0 一致)

- AXI Clock:全部采用 PHY 提供的 125 MHz,禁用异步时钟域

- AXI DBI:不使用

- AXI Master IDs:保留默认 32;注意与 AXI Slave 侧匹配

- 未提及项保持默认或取消勾选

2.7 Device-Wide Non-PCIe Config

多数配置无需启用;关闭 ASPM 以降低调试复杂度。

2.8 Advanced AXI Config

一般保持默认;与 AXI Slave 连接时须确保参数一致。

2.9 Device-Wide PCIe Features

- MSI / MSI-X

本项目关注高速串行通信本身,不涉及中断;故不启用。 - PCIe Capability

大部分选项无需开启;关闭 ASPM。 - VC(Virtual Channel):不使用

- AtomicOp:不使用

- 其他未列项保持默认或不勾选

2.10 Per-Function PCIe 与 BAR 配置

- Advanced Error Register:ECRC 可开启亦可关闭;需与 VIP 保持一致

- Power Management:不使用低功耗特性

- PCI Register Configuration

- Device ID / Vendor ID 等影响 Linux 驱动匹配,保持默认即可

- Include ROM BAR:不勾选

- BAR Setup(仅使用 BAR0)

- Include BAR_0:勾选

- BAR0 Type:Memory

- BAR0 Bit Size:32-bit

- BAR0 Sizing Scheme:Fixed Mask

- BAR0 Mask:0x3fff(64 KB,避免过大)

- Specify Target Interface For BAR0:Target_1(关键;Target_0 走 LBC,仅用于配置)

- VF Sizing Scheme:Fixed Mask

- 其余 BAR 不启用

2.11 Advanced RAM Config

保持默认;Latency 设为 1 cycle。综合到 FPGA 时将自动映射至 BRAM。

2.12 Advanced PHY Config

保持默认设置。

2.13 其余未列配置

可全部保留默认或不勾选。

2.14 Create Gate-Level Netlist

后续将在 FPGA 上与 Xilinx PCIe PHY 联合仿真,不涉及 ASIC 后端。

2.15 代码生成

点击 Apply 后,配置工具将在项目 src 目录生成所需代码。

PCIe IP配置和编辑器截图