数字部分 3.2 PC Ie Vip调试经验

PCIe SerDes 全流程实战

数字部分:PCIE VIP 调试经验

1 Synopsys PCIe IP 配置与代码

- 在快速验证阶段,最容易出现问题的通常是 配置、复位与时钟。务必反复参考 PCIe IP 用户手册及相关标准。

- Synopsys PCIe IP 及其示例工程提供了多种复位方案和时钟域选择。

- 为了简化验证,本项目选用外部 100 MHz 晶振接入 PHY,并由 PHY 输出 125 MHz PHY Clock。整个 PCIe IP 统一使用 125 MHz 时钟,系统仅包含两个时钟域。

- 复位采用三级策略:硬件复位(PCIe 复位引脚)、PHY 复位、PCIe IP 复位。

2 PCIe VIP 的使用

- PCIe VIP 采用软硬件协同方式,模拟 Root Complex 端,可在电路层仿真电气与协议层,同时通过软件代码灵活设置测试场景。

- 阅读 PCIe VIP 与 UVM 相关文档,熟悉 VIP 的接口及用法。

- 合理配置 VIP 并利用其日志功能,可显著提升调试效率。

3 VCS、Verdi、WaveTools 等工具

- 熟悉 VCS 各类编译/仿真参数,例如增量编译选项 -Mupdate,以及

+incdir+的头文件路径处理规则。 - 即使示例工程中的部分顶层端口未使用,也应显式拉高/拉低;悬空信号易导致 X/Z 传播。

- Verdi:可以保存

signal.rc,通过 Shift + L 重新加载 FSDB;在 File 选项卡中可导出所选信号列表。 - WaveTools:支持将 FSDB 转换为 VCD,便于后续 Python 脚本分析。

4 AXI4-Full 协议要点

- 基本信号:

data、addr、reset、clock - 控制信号:

ready、valid、last - ID 信号:

wid、rid、bid - 突发类型:

burst - 其他信号:

qos、csysreq、csysack - 与 PCIe 交互的扩展信号:各类

msic_*信号,携带 TLP 相关信息。

5 日志分析

- 优先查看 VIP 生成的日志,可在无需波形的情况下定位部分问题。

compile.log:记录编译期警告与错误,部分 warning 可能隐藏潜在缺陷。sim.log:输出仿真期间的关键信息。transaction.log:记录 VIP 侧的 TLP、DLLP 事务,便于协议层排查。symbol_log:展示 MAC/PIPE 层的packet信息。

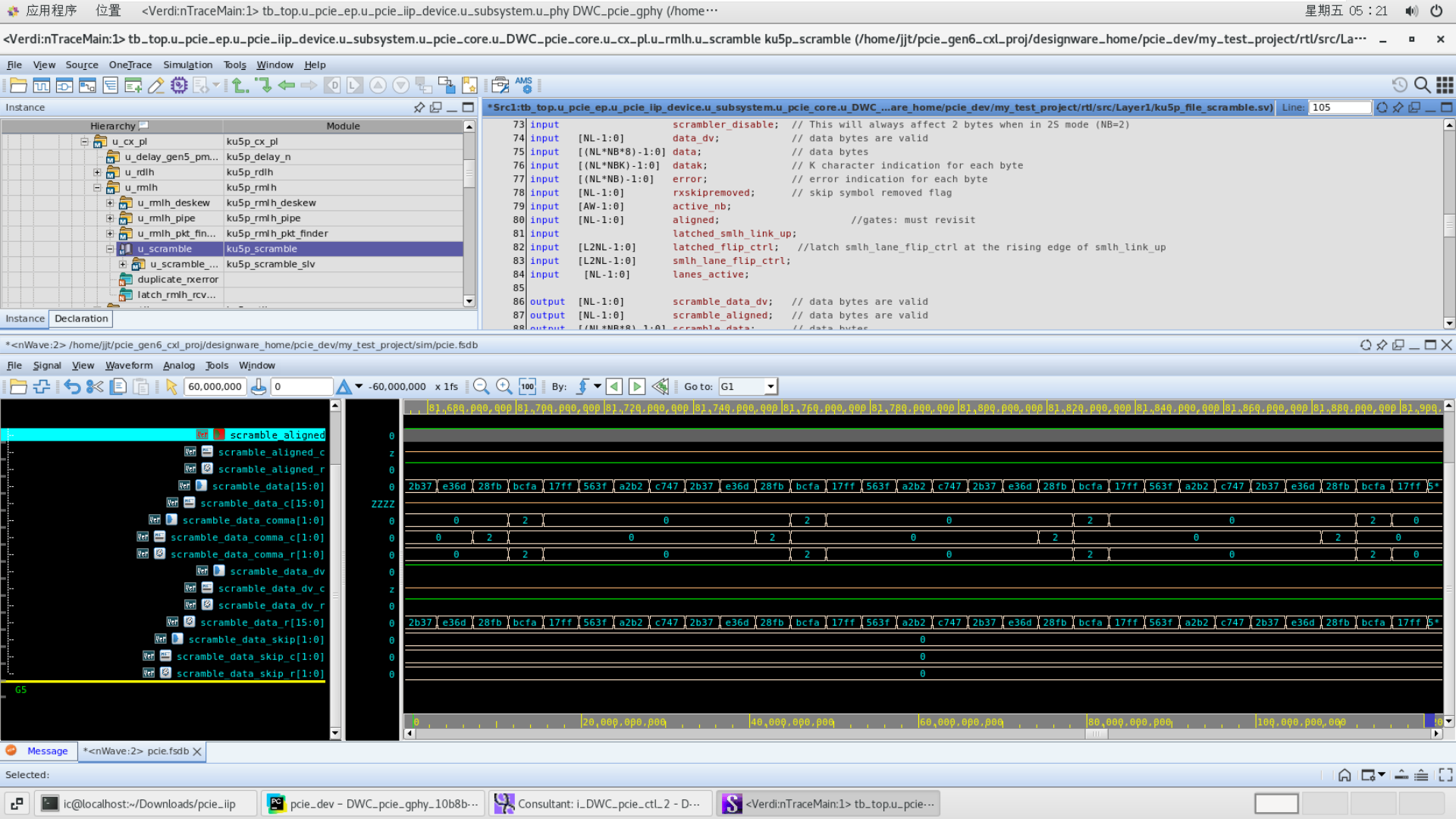

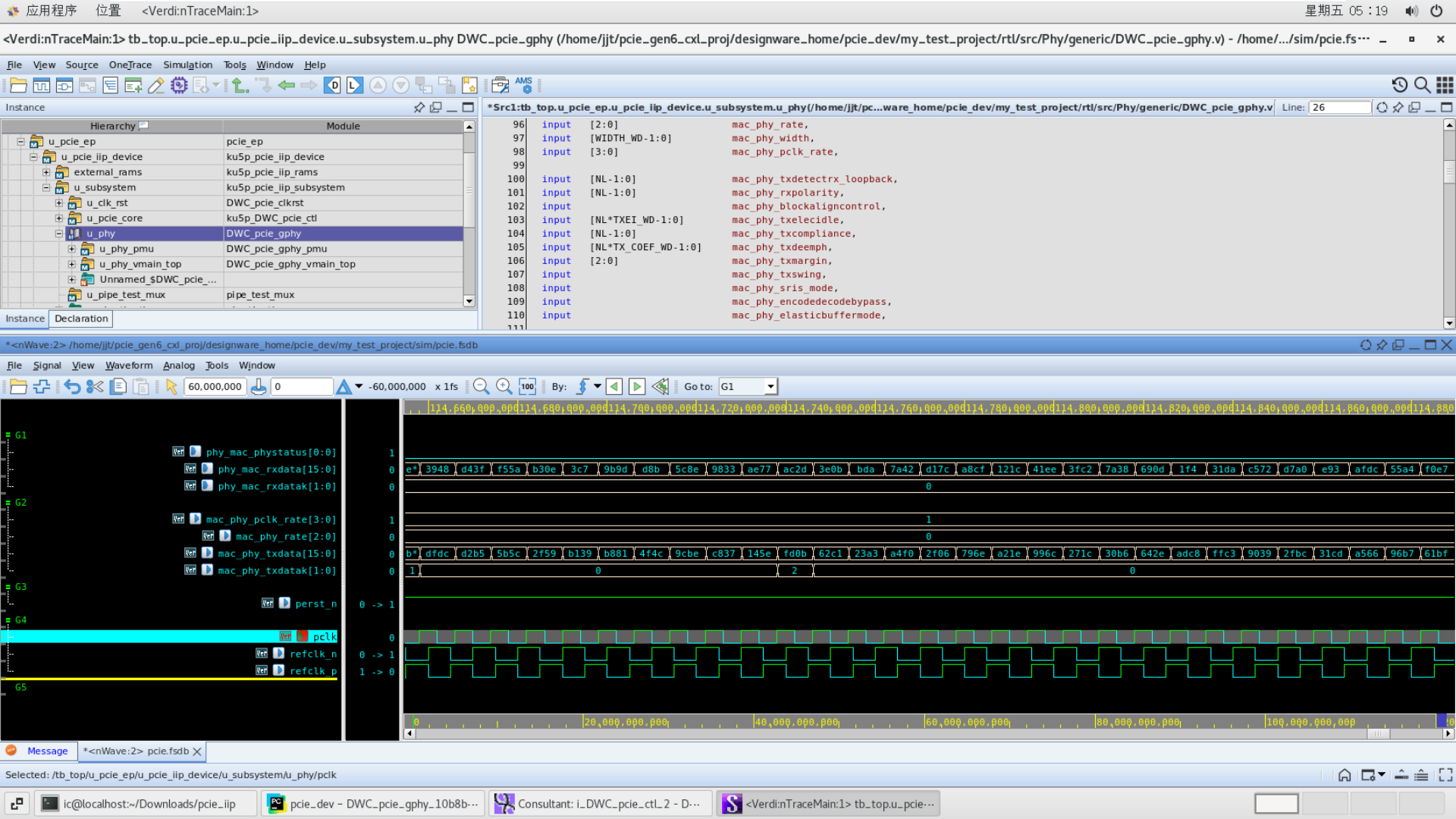

6 Verdi 波形观测

- 在 Endpoint 侧,可直接参考 PCIe IP 提供的示例代码层次。

- 常用层级路径:

/tb_top/spd_0/m_ser/port0/tl0— Transaction Layer

/tb_top/spd_0/m_ser/port0/dl0— Data Link Layer

/tb_top/spd_0/m_ser/port0/pl0— Physical Layer

/tb_top/spd_0/m_ser/port0/ser_if— SerDes 接口信号 - 其他信号说明请参阅 Synopsys PCIe IP 与 VIP 文档。

7 Verdi波形截图