模拟部分 4.1 Cml Tx Driver电路

PCIe SerDes 全流程实战

模拟部分——CML TX Driver电路

本项目主要讲解模拟serdes电路结构,具体器件参数选取不适用于实际流片。

1 电路作用

PCI Express 物理层要求在 50 Ω 单端、100 Ω 差分端口上提供约 0.8 Vpp (具体参考PCIe规范)。本设计在28 nm CMOS 工艺下实现 16 Gb/s NRZ 发送机,最终驱动级采用PMOS‑CML 架构,并内置两只 49.86 Ω 终端电阻以匹配外部 100 Ω 差分通道。 该电路同时实现了3Tap FFE,其抽头参数使用PCIe规范文档的参考值[0 0.75 -0.25]

2 电路结构

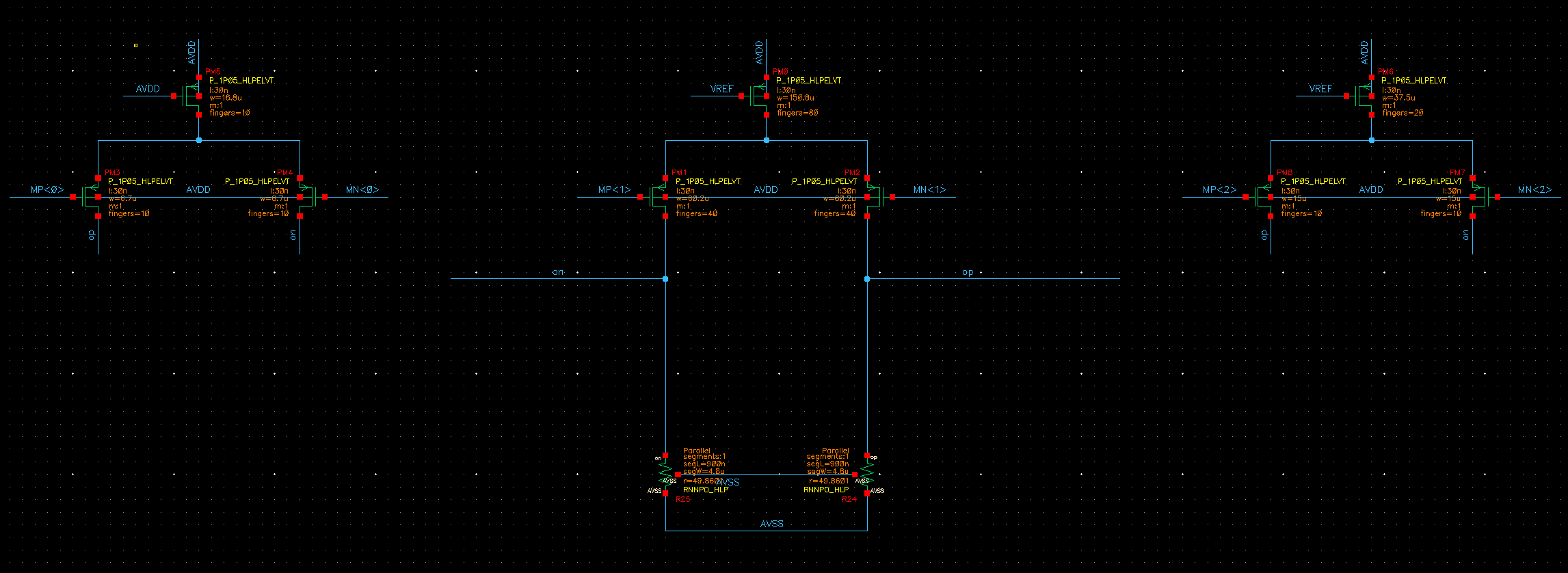

CML_pmos将三路经 MUX预驱放大的电流控制信号 MN<0:2>,MP<0:2> 转换为差分输出 op/on 电流。- 每级由两只信号开关PMOS管和一只PMOS管作为电流源组成。

- R24/R25 = 49.86 Ω 提供发送端阻抗匹配并完成电压转换。

- 因为pre cursor系数为0,PMOS栅级接AVDD用于关闭电流源MOS管。

3 器件参数计算要点

CML 本身主要是电流类型的电路,计算围绕着电流计算展开

- 首先计算MOS管的gm/Id曲线,MOS管能提供多大电流

- 通过Vpp和终端电阻计算CML所需电流

- 计算3Tap对应的电流系数,如果系数为负,需要电路反接

- 通过以上计算结果,计算MOS管的W,L,multiplier,fingers

- 在高频情况,需要考虑零极点的处理,可以使用电感峰化等电路提高带宽。

4 电路截图