模拟部分 4.2 Serial32 2 Tree电路

PCIe SerDes 全流程实战

模拟部分——Serial32_2_Tree电路

本项目主要讲解模拟serdes电路结构,具体器件参数选取不适用于实际流片。

1 电路作用

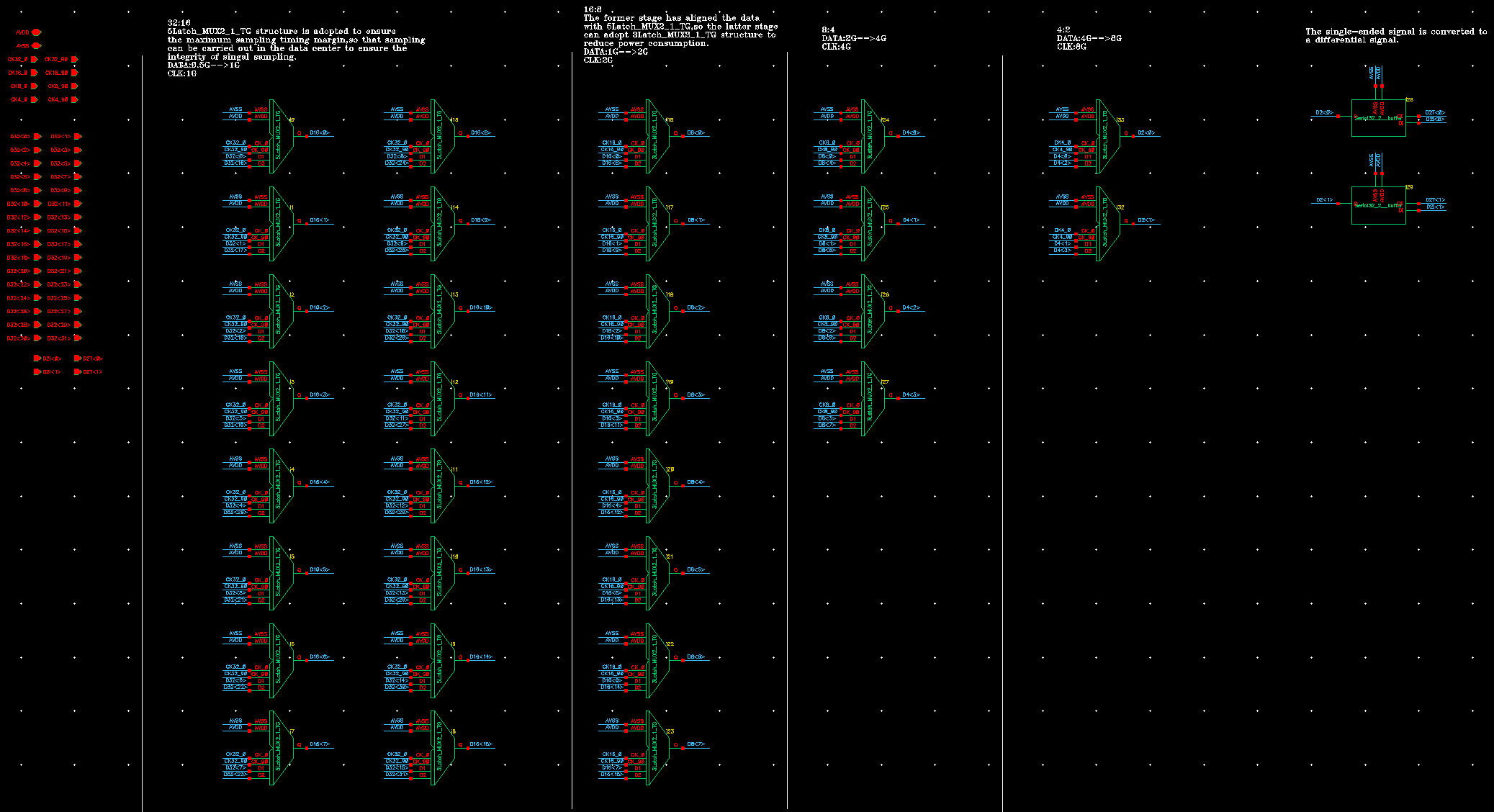

在 16 Gb/s NRZ PCIe 物理层发射机中,Serial32 → 2 Tree 担任最后一级并-串转换。它将 32 bit 并行数据(500M clk)依次压缩为 16 / 8 / 4 / 2 bit,再交由 8 GHz 双相时钟(8G clk)完成 2:1 终端串化,输出半速(half-rate)差分码流供后级High Speed MUX 和 CML 驱动器发送。

2 电路结构

32 并行位经五级 2:1 MUX 依次收敛为 2 bit,再送入差分驱动器。各级输入时钟频率如下:

| 级别 | 并行度 | 时钟标号 | 频率 (典型) |

|---|---|---|---|

| 0 | 32 | CK32 | 500 MHz |

| 1 | 16 | CK16 | 1 GHz |

| 2 | 8 | CK8 | 2 GHz |

| 3 | 4 | CK4 | 4 GHz |

| 4 | 2 | CK8 | 8 GHz |

最后2bit信号,通过Serial32_2__buffer电路,生成差分信号供后级 CML使用,并且提高MOS管宽度,匹配后级电路,提高驱动速度。

3 器件参数计算要点

Serializer电路本身偏向数字电路,可参考工艺库自带数字电路器件参数,要注意时序裕量的计算。

4 电路截图