模拟部分 4.3 Half Rate NRZ 16 G电路

PCIe SerDes 全流程实战

模拟部分——Half_rate_NRZ_16G电路

本项目主要讲解模拟serdes电路结构,具体器件参数选取不适用于实际流片。

1 电路作用

Half_rate_NRZ_16G 实现一条半速率(half-rate)发送链:内部工作时钟 8 GHz,输出数据速率 16 Gb/s。除前两节已介绍的 CML TX Driver 与 Serial 32-to-2 Tree 外,还包括以下功能模块:

- 使用 C2MOS 锁存器产生 3 Tap FFE 所需的三相数据;

- 通过 High_Speed_MUX 完成最终 2-选-1 复用;

- 高速信号在 High_Speed_Pre_Driver 中经电流倍增,以获得足够的驱动能力。

2 电路结构(除去之前讲解的电路)

2.1 C2MOS 锁存器

C2MOS_Latch 采用互补反相时钟控制的对称 PMOS / NMOS 结构:

- 时钟高电平期间采样输入数据;

- 时钟低电平期间保持前一时刻数据。

2.2 High_Speed_MUX

High_Speed_MUX_2_1 是 16 Gb/s NRZ 串行器最前端的 2-选-1 复用器。利用互补时钟相位将一个 125 ps 周期划分为两个 62.5 ps 时间窗:

• CLK = 0,CLKI = 1 → 选通 D0

• CLK = 1,CLKI = 0 → 选通 D1

选择后的数据经对称 NMOS-PMOS 传输门送至节点 OUT,再通过三级尺寸递增的 CMOS 反相器链缓冲后输出到 VOUT,保证在 16 Gb/s 及以上速率下的摆幅和驱动能力。

2.3 High_Speed_Pre_Driver

High_Speed_Pre_Driver 采用电流倍增拓扑:从最小驱动单元(宽度 8 µm)开始,每级翻倍直至 128 µm,以满足后级 CML Driver 的驱动需求。

3 不足与缺陷

目前电路已实现基本功能,但仍存在以下问题:

- 若干关键细节尚未充分优化;

- 信道与均衡的仿真尚未完成。

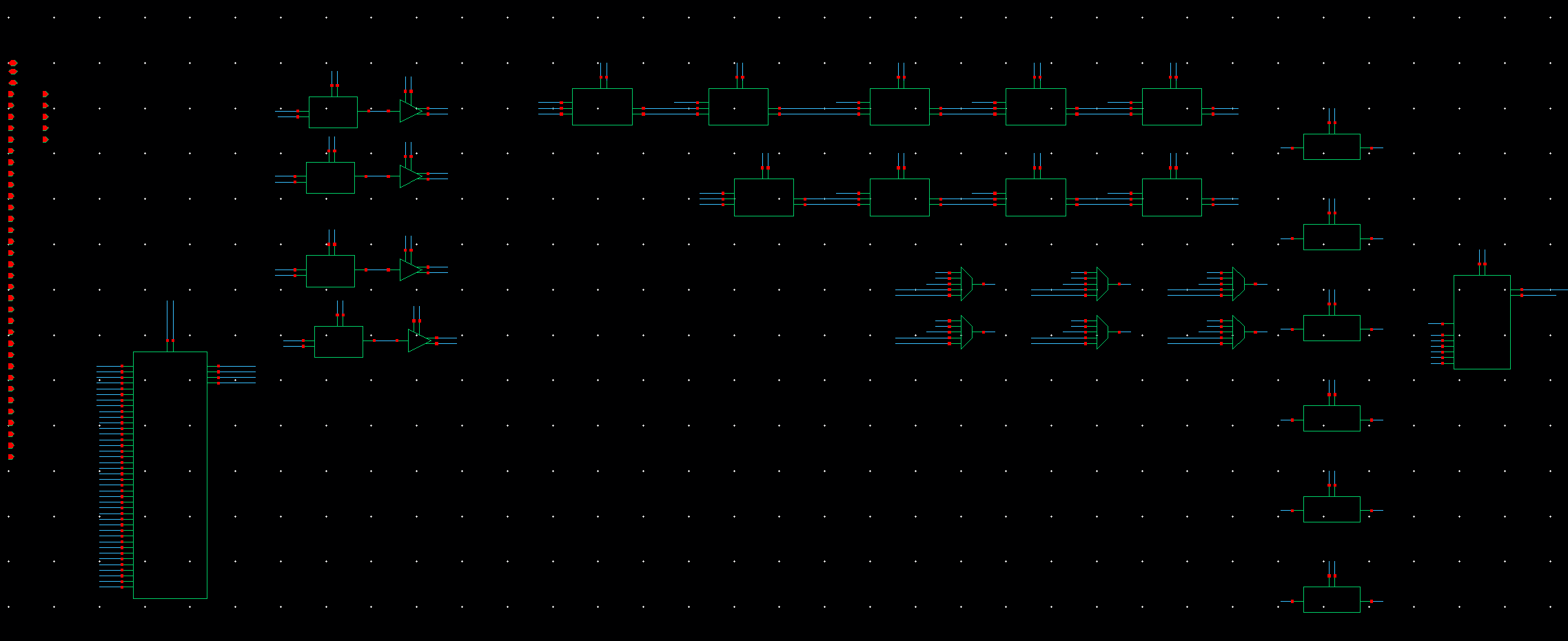

4 电路截图

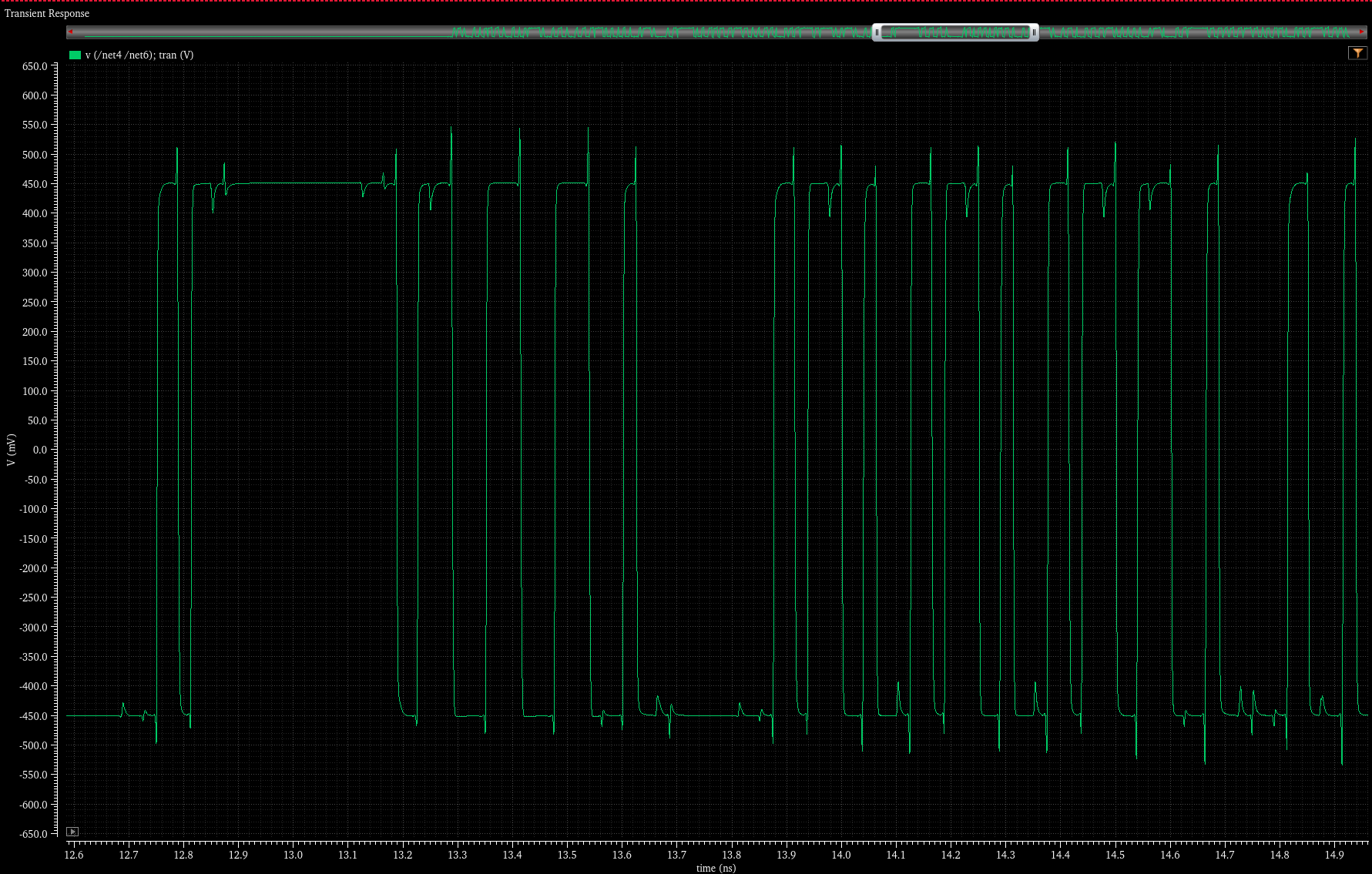

5 仿真截图(未经过均衡和信道模型)